简介

一个按钮,8位动态显示数码管(有小数点,段选为8位,位选与段选均为低电平有效),时钟信号(50MHz)

这是一份简单的数电大作业,原本想做一个简易计算器的,但是由于本人拖沓,到ddl了也只做了一点点,只好改变目标,改做计算器。

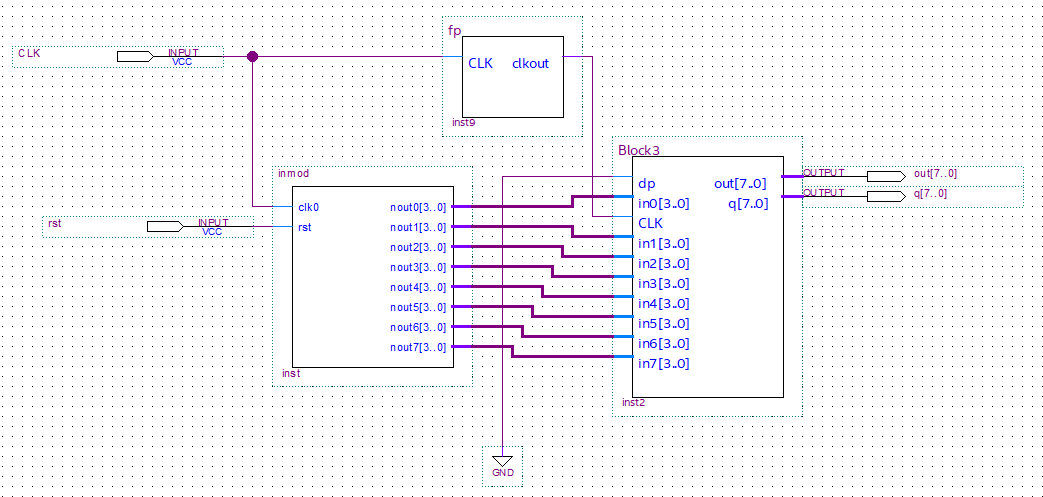

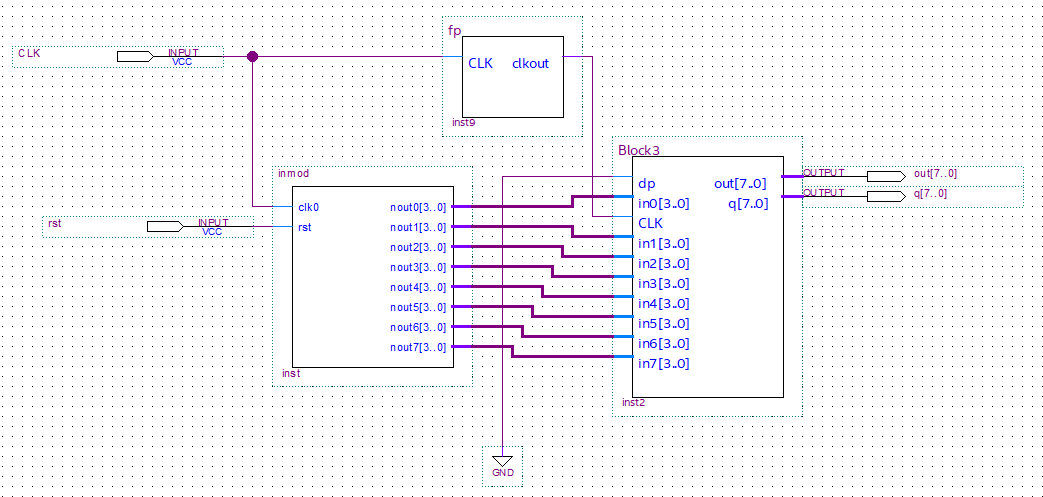

基本模型

左边是输入模块,上面是一个分频器,右边是输出模块。

输入模块

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

| module inmod(clk0,rst,nout0,nout1,nout2,nout3,nout4,nout5,nout6,nout7);

input clk0;

input rst;

output reg [3:0] nout0,nout1,nout2,nout3,nout4,nout5,nout6,nout7;

reg [31:0] n;

reg [25:0] timer;

reg [5:0] sec_count;

reg [5:0] min_count;

reg [4:0] hour_count;

reg [6:0] day_count;

reg clk;

initial

begin

timer=0;

n=0;

clk=0;

sec_count=0;

min_count=0;

hour_count=0;

day_count=0;

end

always @(posedge clk0)

begin

if(timer==2475_0000)

begin

clk=!clk;

timer<=0;

end

else

timer<=timer+1;

end

always @(posedge clk or posedge rst) begin

if (rst) begin

n <= 0;

sec_count <= 0;

min_count <= 0;

hour_count <= 0;

day_count <= 0;

end else begin

sec_count <= sec_count + 1;

if (sec_count == 59) begin

sec_count <= 0;

min_count <= min_count + 1;

if (min_count == 59) begin

min_count <= 0;

hour_count <= hour_count + 1;

if (hour_count == 23) begin

hour_count <= 0;

day_count <= day_count + 1;

end

end

end

case(sec_count % 10)

0:nout7<=4'b0000;

1:nout7<=4'b0001;

2:nout7<=4'b0010;

3:nout7<=4'b0011;

4:nout7<=4'b0100;

5:nout7<=4'b0101;

6:nout7<=4'b0110;

7:nout7<=4'b0111;

8:nout7<=4'b1000;

9:nout7<=4'b1001;

default:nout7<=4'b0000;

endcase

case(sec_count / 10)

0:nout6<=4'b0000;

1:nout6<=4'b0001;

2:nout6<=4'b0010;

3:nout6<=4'b0011;

4:nout6<=4'b0100;

5:nout6<=4'b0101;

6:nout6<=4'b0110;

default:nout6<=4'b0000;

endcase

case(min_count % 10)

0:nout5<=4'b0000;

1:nout5<=4'b0001;

2:nout5<=4'b0010;

3:nout5<=4'b0011;

4:nout5<=4'b0100;

5:nout5<=4'b0101;

6:nout5<=4'b0110;

7:nout5<=4'b0111;

8:nout5<=4'b1000;

9:nout5<=4'b1001;

default:nout7<=4'b0000;

endcase

case(min_count / 10)

0:nout4<=4'b0000;

1:nout4<=4'b0001;

2:nout4<=4'b0010;

3:nout4<=4'b0011;

4:nout4<=4'b0100;

5:nout4<=4'b0101;

6:nout4<=4'b0110;

default:nout4<=4'b0000;

endcase

case(hour_count % 10)

0:nout3<=4'b0000;

1:nout3<=4'b0001;

2:nout3<=4'b0010;

3:nout3<=4'b0011;

4:nout3<=4'b0100;

5:nout3<=4'b0101;

6:nout3<=4'b0110;

7:nout3<=4'b0111;

8:nout3<=4'b1000;

9:nout3<=4'b1001;

default:nout3<=4'b0000;

endcase

case(hour_count / 10)

0:nout2<=4'b0000;

1:nout2<=4'b0001;

2:nout2<=4'b0010;

default:nout2<=4'b0000;

endcase

case(day_count % 10)

0:nout1<=4'b0000;

1:nout1<=4'b0001;

2:nout1<=4'b0010;

3:nout1<=4'b0011;

4:nout1<=4'b0100;

5:nout1<=4'b0101;

6:nout1<=4'b0110;

7:nout1<=4'b0111;

8:nout1<=4'b1000;

9:nout1<=4'b1001;

default:nout1<=4'b0000;

endcase

case(day_count / 10)

0:nout0<=4'b0000;

1:nout0<=4'b0001;

2:nout0<=4'b0010;

3:nout0<=4'b0011;

4:nout0<=4'b0100;

5:nout0<=4'b0101;

6:nout0<=4'b0110;

7:nout0<=4'b0111;

8:nout0<=4'b1000;

9:nout0<=4'b1001;

default:nout0<=4'b0000;

endcase

end

end

endmodule

|

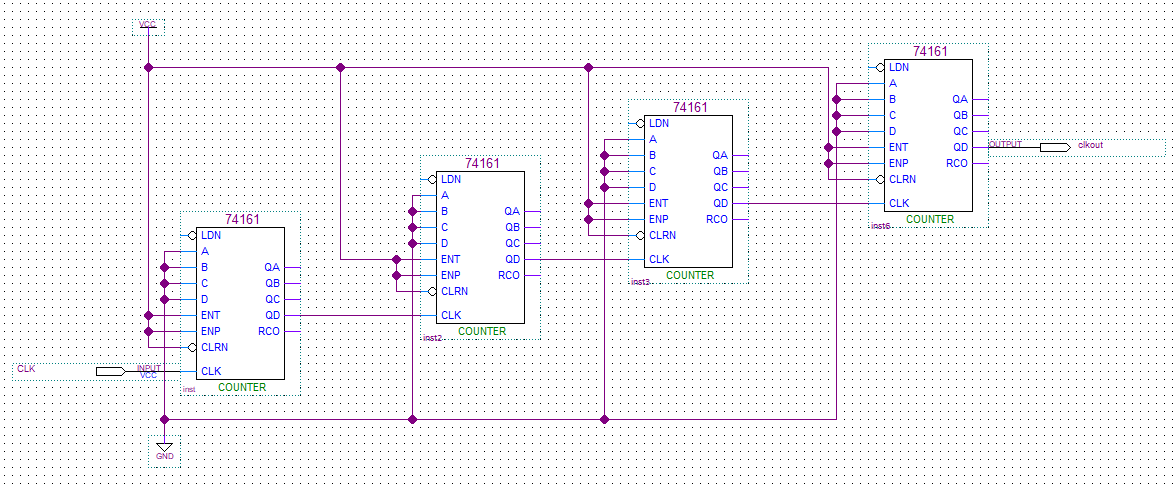

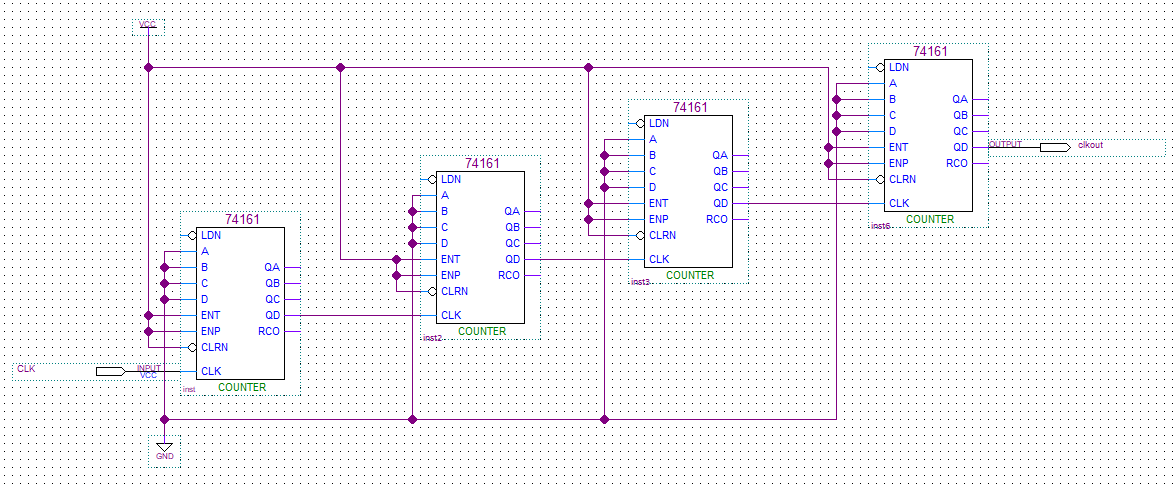

分频模块

4个74161无脑分频

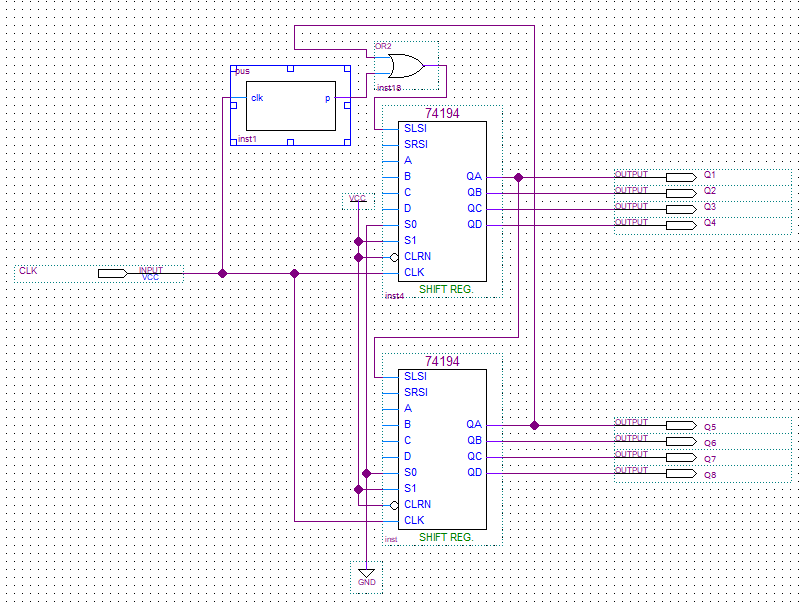

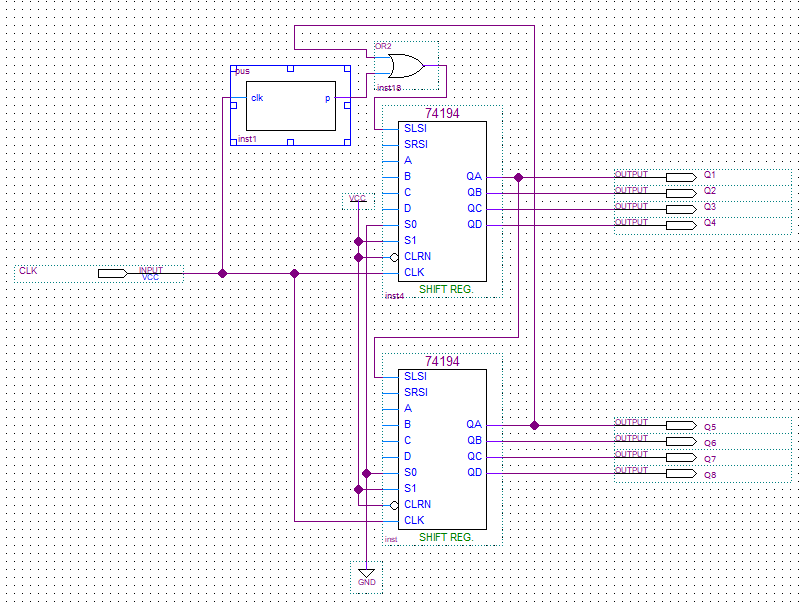

输出模块

思路:8位环形计数器,控制8个7447(plus版),然后把8个7447与起来,就得到了段选,8位环形计数器在控制7447开与关的同时得到了位选

8位环形计数器

额外的pus模块提供一个初始脉冲,用于启动计数器

注意:当8位环形计数器左移过快时,8位数码管的显示将会错乱,于是有了4个74161构成的分频模块

pus模块

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

| module pus (

input clk,

output reg p

);

reg pu;

initial

pu<=0;

always @(posedge clk) begin

if (!pu) begin

p <= 1;

pu <= 1;

end else begin

p <= 0;

end

end

endmodule

|

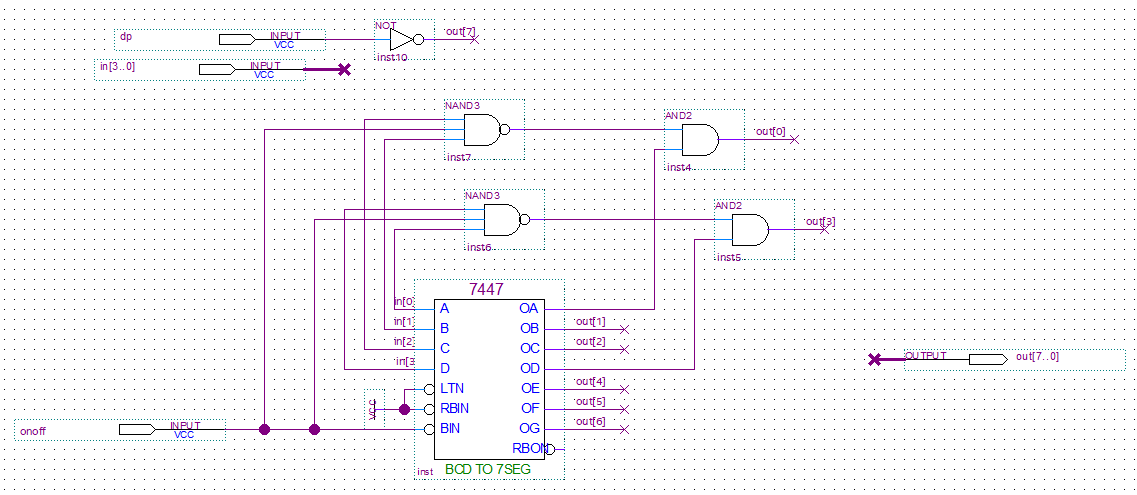

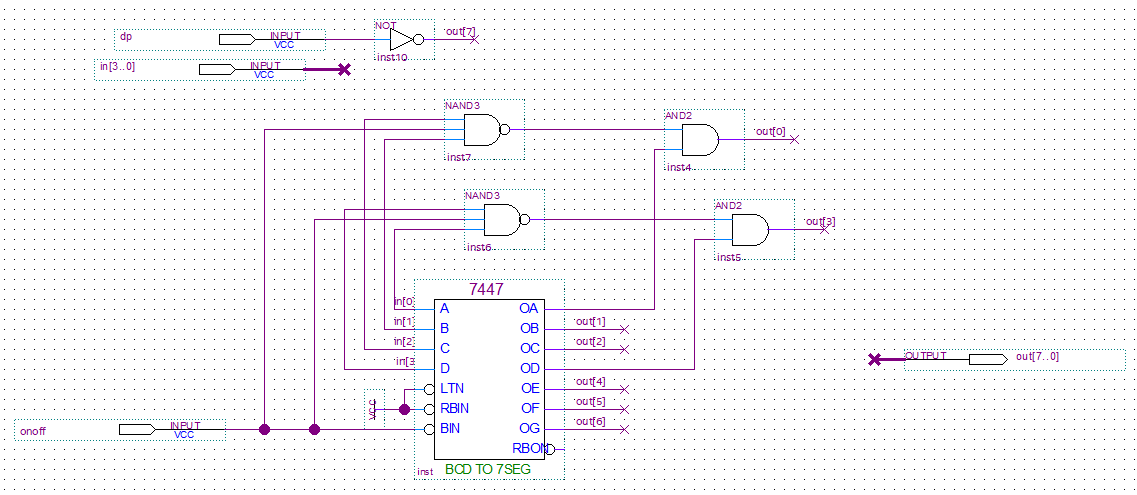

7447plus

out[7]为小数点位

out[0]和out[3]是最上面一横和最下面一横,7447真值表里的6和9各少了一横,需要补上

与门

1

2

3

4

5

6

7

8

| module ands(in1,in2,in3,in4,in5,in6,in7,in8,out);

input [7:0] in1,in2,in3,in4,in5,in6,in7,in8;

output reg [7:0] out;

always@(in1,in2,in3,in4,in5,in6,in7,in8,out)

begin

out<=((in1&in2)&(in3&in4))&((in5&in6)&(in7&in8));

end

endmodule

|